## Contents

| Cover                                                                                                                                                                                                                                                                    |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <u>Title Page</u>                                                                                                                                                                                                                                                        |

| Copyright                                                                                                                                                                                                                                                                |

| About the Authors                                                                                                                                                                                                                                                        |

| <u>Preface</u>                                                                                                                                                                                                                                                           |

| <u>Acknowledgements</u>                                                                                                                                                                                                                                                  |

| <u>Nomenclature</u>                                                                                                                                                                                                                                                      |

| Chapter 1: Warm Up  1.1 Bipolar Junction Transistors 1.2 Metal-Oxide Semiconductor Field-Effect Transistor 1.3 Diode 1.4 Resistor 1.5 Device Matching 1.6 Simulation Models for Circuit Design 1.7 Noise 1.8 Fabrication Technology 1.9 Book Organization 1.10 Exercises |

#### References

## <u>Chapter 2: Voltage Reference</u>

- 2.1 Performance Measures

- 2.2 Other Design Considerations

- 2.3 Summary

- 2.4 Exercises

- <u>References</u>

## **Chapter 3: Bandgap Voltage Reference**

- 3.1 Widlar Bandgap Voltage Reference Circuit

- 3.2 Drain Voltage Equalization Current Mirror

- 3.3 Major Circuit Elements

- 3.4 Complete Layout

- 3.5 Summary

- 3.6 Exercises

- References

## <u>Chapter 4: Error Sources in Bandgap</u> <u>Voltage Reference Circuit</u>

- 4.1 Non-Ideal Opamp

- 4.2 Current Mirror Mismatch

- 4.3 Bipolar Transistor

- 4.4 Resistor Variation

- 4.5 Power Supply Variation

- 4.6 Output Loading

- 4.7 Output Noise

- 4.8 Voltage Reference Circuit Trimming

- 4.9 Summary

# 4.10 Exercises References

## **Advanced Voltage Reference Circuits**

## <u>Chapter 5: Temperature Compensation</u> <u>Techniques</u>

5.1 V<sub>RF</sub> - Δ V<sub>RF</sub> Compensation

5.2 Widlar PTAT Current Source and V<sub>RF</sub>

**Compensation**

5.3 V<sub>ss</sub> Based Temperature Compensation

5.4 Summary

5.5 Exercises

**References**

## <u>Chapter 6: Sub-1V Voltage Reference</u> <u>Circuit</u>

6.1 Sub-1V Output Stage

6.2 Voltage Headroom in Opamp Based β – multiplier Voltage Reference Circuit

<u>6.3 Sub-1V Bandgap Voltage Reference by</u> Resistive Division

6.4 Peaking Current Source and V<sub>BE</sub> Compensation

6.5 Weighted <u>A V<sub>cs</sub> Compensation</u>

6.6 Summary

6.7 Exercises

References

## <u>Chapter 7: High Order Curvature</u> <u>Correction</u>

- 7.1 Compensation Order

- 7.2 Second Order Temperature Compensation

- 7.3 BJT Current Subtraction

- 7.4 Piecewise Linear Compensation

- 7.5 Sum and Difference of Sources with Similar Temperature Dependence

- 7.6 Summary

- 7.7 Exercises

- References

# <u>Chapter 8: CMOS Voltage Reference</u> without Resistors

- 8.1 Generation of Weighted PTAT Source By Inverse Functions

- 8.2 Resistorless Voltage and Current Sources

- 8.3 First Order Compensated Resistorless

Bandgap Voltage Reference Circuit

- 8.4 Resistorless Sub-Bandgap Reference Circuit

- 8.5 Summary

<u>References</u>

## A: SPICE Model File

## B: SPICE Netlist of Voltage Reference Circuit

#### Index

## CMOS VOLTAGE REFERENCES

# AN ANALYTICAL AND PRACTICAL PERSPECTIVE

Chi-Wah Kok and Wing-Shan Tam

Canaan Microelectronics Corporation Ltd, Hong Kong

## This edition first published 2013 © 2013 John Wiley & Sons Singapore Pte. Ltd.

#### Registered office

John Wiley & Sons Singapore Pte. Ltd., 1 Fusionopolis Walk, #07-01 Solaris South Tower, Singapore 138628

For details of our global editorial offices, for customer services and for information about how to apply for permission to reuse the copyright material in this book please see our website at <a href="https://www.wiley.com">www.wiley.com</a>.

All Rights Reserved. No part of this publication may be reproduced, stored in a retrieval system or transmitted, in any form or by any means, electronic, mechanical, photocopying, recording, scanning, or otherwise, except as expressly permitted by law, without either the prior written permission of the Publisher, or authorization through payment of the appropriate photocopy fee to the Copyright Clearance Center. Requests for permission should be addressed to the Publisher, John Wiley & Sons Singapore Pte. Ltd., 1 Fusionopolis Walk, #07-01 Solaris South Tower, Singapore 138628, tel: 65-66438000, fax: 65-66438008, email: enquiry@wiley.com.

Wiley also publishes its books in a variety of electronic formats. Some content that appears in print may not be available in electronic books.

Designations used by companies to distinguish their products are often claimed as trademarks. All brand names and product names used in this book are trade names, service marks, trademarks or registered trademarks of their respective owners. The Publisher is not associated with any product or vendor mentioned in this book. This publication is designed to provide accurate and authoritative information in regard to the subject matter covered. It is sold on the understanding that the Publisher is not engaged in rendering professional services. If professional advice or

other expert assistance is required, the services of a competent professional should be sought.

#### Library of Congress Cataloging-in-Publication Data

CMOS voltage references : an analytical and practical perspective / Chi-Wah Kok, Wing-Shan Tam. - First edition. pages cm

Includes bibliographical references and index. ISBN 978-1-118-27568-9 (hardback)

1. Voltage references. 2. Electric circuit analysis. 3. Electric circuits-Design and construction. I. Kok,

Chi-Wah. II. Tam, Wing-Shan. III. Title: Voltage reference.

TK454.C628 2013 621.3815′28-dc23 2012030274

ISBN: 9781118275689

## **ABOUT THE AUTHORS**

Chi-Wah Kok was born in Hong Kong. He was granted a PhD degree from the University of Wisconsin Madison. Since 1992, he has been working with various semiconductor companies, research institutions, and universities, which include AT & T Labs Research, Holmdel, SONY U.S. Research Labs, Stanford University, Hong Kong University of Science and Technology, Hong Kong Polytechnic University, City University of Hong Kong, Lattice Semiconductor, etc. In 2006, he founded Canaan Microelectronics Corp Ltd., a fabless IC company with products in mixed signal IC for consumer electronics. Dr. Kok embraces new technologies to meet the fast changing market requirements. He has extensively applied signal processing techniques to improve the circuit topologies, designs, and fabrication technologies within Canaan. This includes the application of semidefinite to circuit design optimization, programming algebra switched capacitor topologies in circuit improvement, and nonlinear optimization methods optimize high voltage MOSFET layout and fabrication.

**Wing-Shan Tam** was born in Hong Kong. She received her BEng degree in electronic engineering from The Chinese University of Hong Kong, MSc degree in electronic and information engineering from The Hong Kong Polytechnic University, and PhD degree in electronic engineering from the City University of Hong Kong in 2004, 2007, and 2011, respectively. Currently, she is the Engineering Manager of Canaan Microelectronics Corp Ltd. Her research interests include mixed-signal integrated circuit design for data conversion and power-management.

#### **PREFACE**

This book has a genesis: It started as internal training material for engineers working in Canaan Microelectronics Corp. Ltd. It is also a monograph because it presents the outcome of our research and teaching activities in the field of temperature independent circuit design at both the Canaan Microelectronics Corp. Ltd. and the City University of Hong Kong. Many unpublished works are included in this book. Numerous design examples are also presented together with detailed discussions on design principles, performance analysis, and the potential problems of each circuit topology. This book is intended to be course material for senior and graduate level courses, training material for engineers, and also a reference text for readers who are working in the field of temperature independent circuit design.

The book is divided into eight chapters. The first chapter offers an introduction of device physics focusing on the properties of individual devices. temperature introduces just enough material for voltage reference circuit design and analysis. Details of general device physics may be gathered from existing literature, such as the textbooks by Chenming C. Hu, (Modern Semiconductor Devices for Integrated Circuits, Prentice Hall, 2010), and S.M. Sze, (Physics of Semiconductor Devices, Wiley, 1969) that offer detailed discussions on the device physics for bipolar transistors, MOS transistors, and other passive components manufactured in the CMOS process. Besides the physics, towards the end of Chapter 1, we also discuss practical issues in CMOS circuit design. The device matching problem is introduced. Computer simulation for circuit design with process variations is discussed. Finally, the device noise

models that describe the noises associated with CMOS devices are presented. Chapter 2 presents the performance characterization of voltage reference circuits. The presented characterization will be used throughout the book in the analytical discussions and performance comparisons of individual voltage reference circuits. A general voltage reference circuit framework of opamp based β-multiplier bandgap voltage reference is presented in Chapter 3. The presented voltage reference circuit is silicon proven, and has been applied to a power management IC of Canaan Microelectronics Corp. Ltd.: the micrograph of the die is shown on the front page of this book. Every building block within the voltage reference circuit is discussed analytically together with layout details. Various error sources of the circuit are identified, and analyzed in Chapter 4. Methods to remedy each problem together with their pros and cons are discussed in detail in Chapter 4. The basic PTAT-CTAT compensation technique temperature discussed Chapter 4 will be extended to voltage reference circuits various temperature dependent devices topologies in Chapter 5. Analytical derivation to determine the component values of each device within the voltage reference circuit, together with the important design considerations of each circuit topology will be and discussed. Chapter 6 discusses the design of voltage reference circuits with sub-1V supply, and voltage reference circuits with sub-1V reference voltage. Notice that the design of the voltage reference circuit with a sub-1V reference voltage is different from that of the voltage reference circuit with a sub-1V supply voltage. A voltage reference circuit with a sub-1V supply voltage is also a voltage reference circuit with a sub-1V reference voltage. The voltage reference circuit with sub-1V reference voltage being able to operate with a sub-1V supply voltage is important in modern CMOS circuit design where the supply voltage keeps reducing for power reduction and silicon size shrinkage. A number of sub-1V voltage reference circuits will be discussed in this chapter.

High order curvature compensated voltage reference circuits are presented in Chapter 7, which are important to applications that require a reference voltage with low temperature sensitivity. A number of high accuracy voltage reference circuit topologies, including high order curvature compensation, inverted temperature compensation, and piecewise temperature compensation etc. are discussed. This book concludes in Chapter 8 with a discussion on a type of special voltage reference circuit that does not require resistors. Such a voltage reference circuit has the advantage of compact layout. The performance of a resistor free voltage reference circuit can be further optimized with of piecewise temperature applications compensation technique to lower the temperature sensitivity of the circuit. Post-fabrication trimming circuits are discussed to reduce the reference voltage variation.

A detailed summary of the state of the art development with respect to the topic of each chapter is presented in the "Summary" section of each chapter. Homework problems are presented in the "Exercise" section in individual chapter. The homework includes both analytic problems, and SPICE based computer simulation exercises. While the process parameters used in this book and also in developing the exercises may not be the same as those in your institution, it is our hope that the exercises will provide you with general guidelines, analysis, design and layout experience for the design of the voltage reference circuits with the help of SPICE. The experience will further address the performance evaluation of the voltage reference circuit which will help you to achieve a thorough consideration of the voltage reference circuit before the actual design.

The development of voltage reference circuits is still continuing and therefore a book, such as this one, cannot be

definitive or complete. It is hoped, however, that this book will fill an important gap; students embarking upon mixed-signal circuit design should be able to learn sufficient basics before tackling journal papers, researchers and engineers in the field of temperature independent/dependent circuit design should be able to use it as reference to assist their circuit design tasks, and current researchers in the field should be able to get a broad perspective on what has been achieved. The subject area is introduced, some major developments are recorded, and enough successes as well as challenges are noted here for readers to look into other voltage independent/dependent circuit design problems and generate solutions for their own problems.

Chi-Wah Kok and Wing-Shan Tam *February 2012*

## **ACKNOWLEDGEMENTS**

We are in debt to many people, too numerous to mention. To all the scholars who have influenced us, both in person or through their works, we acknowledge our indebtedness and express our great appreciation. Perhaps the most noteworthy was Prof. Hei Wong of the City University of Hong Kong whose knowledge, enthusiasm in advanced microelectronics research and development, and generous support in the course of the development of this book has surely inspired and greatly assisted us. We are proud to say that Prof. Wong is one of our greatest role models.

Dr. Kok would like to take this chance to claim victory in the competition with his wife Dr. Annie Ko on who will be the first to complete his/her second textbook. It was this competition that provided Dr. Kok with the extra boost to get this book finished with his best effort. Dr. Kok is also very happy to collaborate with Dr. Tam on this book project, who has always been his best collaborator in both the academic and business spheres. Dr. Tam is truly indebted and grateful to her parents, Simon Tam and Gloria Lee, for their love, encouragement, and their constant support in all her pursuits, including her PhD study and the completion of this book. Dr. Tam would also like to thank her beloved family, especially her sister and grandmother, who are always willing to share her stress and happiness. Finally, Dr. Tam would like to express her sincere gratitude to Dr. Kok, who introduced her into the world of IC design. Dr. Tam is very grateful for the opportunity to coauthor this book and treasures other aspects of her partnership with Dr. Kok too. Coauthoring a book is never easy. In the course of the development of this book, the authors have learned a lot from each other, and adapted to each others' working and

learning styles. We are looking forward to seeing our excellent partnership extend to future book and other research and development projects.

Despite the assistance, review, overseeing, and editing of so many people, we have no doubt that errors still lurk undetected. These are ours alone, and it is our hope that the reader of this book will discover them and bring them to our attention, so that they all may be eradicated.

Chi-Wah Kok and Wing-Shan Tam

## NOMENCLATURE

**SoC** System-On-Chip

**ATE** Automatic test equipment

**J** Joule

Col CoulombK Kelvin

°C degree Celsius

$V_T$  Thermal voltage, kT/q  $V_{DD}$  Positive supply voltage  $V_{SS}$  Negative supply voltage

BJT Bipolar Junction Transistor

*I<sub>B</sub>* Base Current of Bipolar Transistor

$I_{\scriptscriptstyle C}$  Collector Current of Bipolar Transistor

$I_{\scriptscriptstyle E}$  Emitter Current of Bipolar Transistor

*I<sub>s</sub>* Saturation Current of Bipolar Transistor

$J_c$  Collector Current Density of Bipolar Transistor  $J_s$  Saturation Current Density of Bipolar Transistor

$V_{\rm BE}$  Base-Emitter Voltage of a BJT

$V_{CE}$  Collector-Emitter Voltage of a BJT  $R_B$  Zero-bias base ohmic resistance

$R_E$  Emitter resistance  $R_C$  Collector resistance

$V_{G0}$  Silicon Bandgap Voltage Extrapolated at 0 K

$A_{E}$  Emitter Area of Bipolar Transistor

$W_{\scriptscriptstyle B}$  BJT base width

$\beta$  Forward current gain

$V_D$  Forward-bias diode voltage

MOSFET Metal Oxide Semiconductor Field Effect Transistor

NMOS N-Channel MOSFET

PMOS P-Channel MOSFET

**CMOS** Complementary Metal Oxide Semiconductor

W MOSFET Gate WidthL MOSFET Gate Length

S Channel Width to Length Ratio (W/L) of a MOSFET

$I_{DS}$  Drain to Source Current of a MOSFET

$I_{D.sub}$  Drain to Source Current of a MOSFET biased in subthreshold mode

*I<sub>D lin</sub>* Drain to Source Current of a MOSFET biased in triode mode

$I_{D,sat}$  Drain to Source Current of a MOSFET biased in saturation mode Drain to Source Leakage Current or Off Current of a MOSFET in

cutoff mode

$\hat{I}_{l_{eak}}$  Unit Drain to Source Current Normalized by S

$\zeta$  Subthreshold Slope

$\zeta_n$  Subthreshold Slope of a *n*-channel MOSFET

$\zeta_p$  Subthreshold Slope p-channel MOSFET  $C_p$  Depletion capacitance of a MOSFET

$C_{ox}$  Gate oxide capacitance per unit area of a MOSFET

$t_{ox}$  Thickness of gate oxide

$V_{th}$  Threshold voltage of a MOSFET  $V_{GS}$  Gate source voltage of a MOSFET  $V_{DS}$  Drain source voltage of a MOSFET

$R_{DS,sub}$  Drain source resistance of a MOSFET in subthreshold mode  $V_{DS,sub}$  Drain source voltage of a MOSFET in subthreshold mode

$V_{DS,lin}$  Drain source voltage of a MOSFET in linear mode

$V_{\scriptscriptstyle DS,sat}$  Drain source voltage of a MOSFET in saturation mode

$R_{DS}$  Drain source resistance of a MOSFET

$R_{DS,lin}$  Drain source resistance of a MOSFET in linear mode

$g_{\scriptscriptstyle m}$  Transconductance of a MOSFET

$R_{DS,sat}$  Drain source resistance of a MOSFET in saturation mode

$\mu$  Mobility of the charge carrier

CTAT Complementary to Absolute Temperature

PTAT Proportional to Absolute Temperature

$V_{\text{CTAT}}$  CTAT Voltage  $I_{\text{CTAT}}$  CTAT Current  $V_{\text{PTAT}}$  PTAT Voltage  $I_{\text{PTAT}}$  PTAT Current

$V_{_{IN}}$  Input voltage to the voltage reference circuit

$V_{IN(nom)}$  Nominal input voltage to the voltage reference circuit

$V_{M(min)}$  Minimum input voltage for proper operation of the voltage

reference circuit

$V_{M(max)}$  Maximum input voltage for proper operation of the voltage

reference circuit

$V_{RFF}$  Output voltage of the voltage reference circuit

$V_{DD(min)}$  Minimum operating supply voltage

$V_{DD(nom)}$  Nominal supply voltage

$V_{REF(nom),T}$  Output voltage of the voltage reference circuit at specific

temperature *T* with respect to a range of input voltages

$V_{REF(min),T}$  Output voltage of the voltage reference circuit at VIN(min) and

temperature T

$V_{REF(max),T}$  Output voltage of the voltage reference circuit at VIN(max) and

temperature T

$V_n$  Noise source

$V_{\scriptscriptstyle REFCOMV}$  Reference voltage generated by conventional  $V_{\scriptscriptstyle BE}$  -  $V_{\scriptscriptstyle T}$  temperature

compensation voltage reference circuit

$V_{DROP}$  Dropout voltage defined as the voltage difference between the

input and output voltage

$T_{nom}$  Nominal temperature

$V_{p}(f)$  Noise voltage at frequency f

$T_{min}$  Minimum temperature for proper operation of the voltage

reference circuit

$T_{max}$  Maximum temperature for proper operation of the voltage

reference circuit

$V_{\text{\tiny REF(nom),V_{IN(nom)}}}$  Output voltage of the voltage reference circuit at nominal input

voltage with respect to a temperature range  $[T_{min}, T_{max}]$

$V_{REF(max),V_{IN(nom)}}$  The maximum output voltage of the voltage reference circuit at

nominal input voltage in the temperature range  $[T_{min}, T_{max}]$

$V_{\scriptscriptstyle REF(min),V_{\scriptscriptstyle IM(pom)}}$  The maximum output voltage of the voltage reference circuit at

nominal input voltage in the temperature range  $[T_{min}, T_{max}]$

$I_q$  The quiescent current of the voltage reference circuit

TC Temperature Coefficient

*PSRR* Power supply rejection ratio

BW System bandwidth of the voltage reference circuit

$V_{os}$  Offset voltage

Power-supply rejection ratio that the variation of the reference

| $S_{\scriptscriptstyle PSRR}$ | voltage with a particular frequency in the input voltage                                                                                             |  |

|-------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| $S_x^y$                       | Sensitivity of parameter $y$ with respect to a change in parameter $x$                                                                               |  |

| $S_{LR}$                      | Linear regulation measure of variation of reference voltage with respect to a charge in input voltage to the voltage reference circuit               |  |

| $S_{TC}$                      | Temperature coefficient measure of variation of reference voltage with respect to a change in operation temperature of the voltage reference circuit |  |

**Table 1** Physical Constant

| Parameter       | Description                                    | Typical Values                 |  |

|-----------------|------------------------------------------------|--------------------------------|--|

| k               | Boltzmann's Constant                           | $1.38 \times 10^2 \text{ J/K}$ |  |

| q               | Electron's Charge                              | 1.62 × 10 <sup>-19</sup> Col   |  |

| $V_{\tau}$      | Thermal Voltage                                | kT/q = 26  mV at  300  K       |  |

| $B_{G0}$        | Silicon Bandgap Voltage<br>Extrapolated at 0 K | 1.206 V                        |  |

| V <sub>BE</sub> | Base Emitter Voltage of NPN                    | 0.73 mV at 300 K               |  |

| $V_{BE}$        | Base Emitter Voltage of PNP                    | 0.76 mV at 300 K               |  |

## Warm Up

The voltage reference circuits discussed in this book require you to work on electron devices by connecting together transistors, resistors, and capacitors. Therefore you need to understand the properties and limitations of each device in some detail. The easiest way to learn about electron devices is to study their physical models, although they are usually very complex. For example, the Gummel and Poon model of a bipolar transistor lists 45 parameters (Gummel and Poon, 1970) and yet still is not accurate enough to simulate the saturation or junction breakdown behaviors. The BSIM 3.3 model of a MOS transistor has more than 50 coefficients (Liu, 2001) not counting noise and gate leakage parameters. Although all of these variables are useful for the design of voltage reference circuits, only very few numbers and equations have to be remembered for creative work, and the shapes of a few dependencies and some qualitative relationships (not how much, but more or less, increasing or decreasing) of these parameters are much more important.

The following sections will present, from the authors' point of view, the most important electron device parameters necessary for voltage reference circuit design. Detailed descriptions of the operations of individual electron device can be found in textbooks on analog circuit design or device modeling (Hu, 2010; Sze, 1969). In particular, a large part of this book presents the design and analysis of a special kind of voltage reference circuit, the bandgap voltage reference. It is useful to know which parameters of the practical model

dominate the behavior of each electron devices in the case of bandgap reference circuit design.

The well-known Gummel and Poon model for bipolar transistors, and BSIM 3.3 model for MOSFETs used in SPICE, will form the basis for the design and analysis of bandgap references. In particular HSPICE (HSPICE® Simulation and Analysis User Guide 2006), a typical SPICE simulator, will be used to produce all the simulation results presented in this book based on a 0.18  $\mu$  m mixed signal CMOS process SPICE model. However, instead of going through SPICE, a minimum set of key parameters will be presented in the following sections which allow us to analytically describe the relation between various electron devices behaviors and their application to temperature insensitive circuit design. We shall start our discussions with the active components first, which include the bipolar transistors, MOSFETs, and diode, and then the passive components, which are the resistors made by different CMOS processes.

## 1.1 Bipolar Junction Transistors

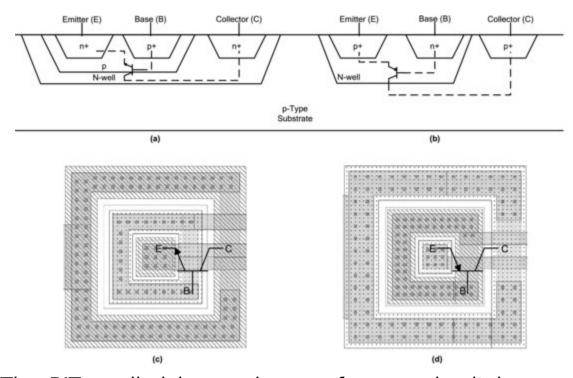

The bipolar junction transistor (BJT), is a vital component in the voltage reference circuit and is commonly used for the generation of temperature dependent voltage, whereas the generation of controllable temperature dependent voltage is the first step towards obtaining a temperature insensitive reference voltage. The BJTs can be implemented in a standard CMOS process. The simplified cross-view of a vertical NPN transistor and a vertical PNP transistor implemented in CMOS process are shown in Figure 1.1(a) and (b), respectively; while Figure 1.1(c) and (d) are the layouts of the transistors in Figure 1.1(a) and (b), respectively. In general, the NPN transistor is preferred because of its higher collector-current efficiency and the highly doped base region which can achieve a low series

base resistance. The awkward effect of the base resistance will be discussed in Section 4.3.2. Besides, there are other limitations on the application of PNP transistor in voltage reference circuit. Consider the vertical PNP transistor illustrated in Figure 1.1(b), where the emitter is formed by a P -type region, the base is formed by a N -well, and the collector is formed by a P -type substrate. There are two limitations imposed on such BJT implementation. First, the collector is formed by the substrate, which is permanently tied to the lowest supply voltage. Second, the current gain of the transistor,  $\beta$ , is very low when compared to its NPN counterpart, which is defined as

$$(1.1)^{\beta=\frac{I_C}{I_B}},$$

with  $I_c$  and  $I_B$  being the currents flowing into the collector and base of the BJT, respectively. To effectively alleviate the base resistance as a source of error in voltage reference circuit design, a high current gain ( $\beta \geq 100$ ) is desired. As a result, the vertical PNP transistor is only applicable to voltage reference circuit design if we make it large to achieve a small base resistance. The last but not least, problem associated with the vertical PNP BJT is that it cannot be used in cascode structure because the collector is required to connect to the ground, and thus cannot be connected to the emitter of another BJT. Despite the above limitations, both the NPN and the PNP BJTs can be used in the voltage reference circuit.

FIGURE 1.1 Integrated bipolar transistor in *N* –well CMOS processes: (a) a vertical NPN transistor and (b) a vertical PNP transistor. Layout examples of (c) NPN transistor in (a) and (d) PNP transistor in (b).

The BJT applied in a voltage reference circuit is usually configured in a diode-connected structure (i.e., the base terminal and the collector terminal are connected together), such that the base-emitter voltage,  $V_{\rm BE}$ , is used to provide a fixed junction voltage. However, the junction voltage is temperature sensitive, and thus cannot be used as reference voltage by itself. The thermal analysis of the BJT, and in particular the  $V_{\rm BE}$ , has been widely discussed in the literature (Massobrio and Antognetti, 1993; Tsividis, 1980). The theory and notation of the NPN transistor are applicable to the PNP transistor with a few obvious modifications. Therefore, all the symbols and notations of these two types of BJTs are used interchangeably in our discussions.

If we neglect the Early effect, the collector current of a NPN transistor biased in the forward active region is given by

$$J_C(T)A_E = J_S(T)A_E \exp\left(\frac{V_{BE}}{V_T}\right),$$

$$(1.2) I_C(T) = I_S(T) \exp\left(\frac{V_{BE}}{V_T}\right),$$

where  $A_{\varepsilon}$  is the base-emitter junction area, T is the absolute temperature in K,  $I_{c}(T)$  is the temperature dependent collector current,  $J_{s}(T)$  is the saturation current density, which relates to the temperature dependent saturation current  $I_{s}(T)$  as  $I_{s}(T) = J_{s}(T) A_{\varepsilon}$ . Finally, the thermal voltage  $V_{\tau}$  is given by

$$(1.3)^{V_T=\frac{kT}{q}},$$

with  $q=1.6\times~10^{19}$  Col being the electron charge, and  $k=1.38\times~10^{23}$  J/° C being the Boltzmann constant. As an example, at  $T=300~\rm K$ ,  $V_r(300)=0.0259~\rm V$ . Without going into further details of the semiconductor physics of BJT, we shall quote the base-emitter voltage function of the BJT from (Johns and Martin 1997).

$$\underbrace{\left( \underbrace{1.4} \right)} V_{BE}(T) = V_{G0} \left( 1 - \frac{T}{T_r} \right) + V_{BE}(T_r) \\ \frac{T}{T_r} - \frac{\rho kT}{q} \ln \left( \frac{T}{T_r} \right) + \frac{kT}{q} \ln \left( \frac{J_C(T)}{J_C(T_r)} \right),$$

where  $V_{co}$  is the bandgap voltage of silicon at 0~K which equals 1.206 V,  $\rho$  is a process dependent temperature constant and equals 1.93 in the process concerned, and  $T_{c}$  is a reference temperature. Consider a temperature dependent collector current that can be modeled as

(1.5)

$$I_C(T) = a \times T^{\theta}$$

,

where a is a constant and  $\theta$  is the order of temperature dependency,  $\theta=0$  implies the collector current is independent with temperature, and  $\theta=1$  implies the collect current varies linearly with temperature, and so on. The collector current density at temperature T with respect to the collector current density at the reference temperature T, is given by

$$(1.6) \frac{J_C(T)}{J_C(T_r)} = \left(\frac{T}{T_r}\right)^{\theta}.$$

We can thus simplify  $V_{RF}(T)$  as

$$(1.7) \ V_{BE}(T) = V_{G0} \left(1 - \frac{T}{T_r}\right) + V_{BE}(T_r) \frac{T}{T_r} - (\rho - \theta) \frac{kT}{q} \ln \left(\frac{T}{T_r}\right).$$

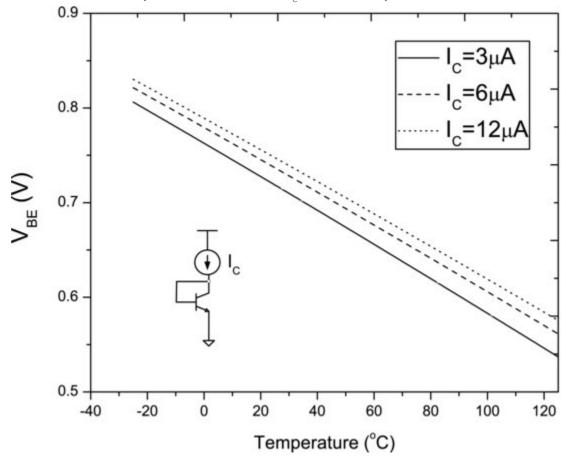

It can be observed that  $V_{\rm RF}(T)$  is nonlinearly related to temperature. Furthermore, because of the  $V_{BE}(T_r)$  term in the above equation,  $V_{RF}(T)$  might vary with the biasing condition (which depends on the collector current) as well as the transistor size (which depends on the emitter area). Figure 1.2 shows the SPICE simulation of the temperature dependency of the  $V_{\scriptscriptstyle BE}$  of a NPN BJT with 25  $\mu$  m  $^{\scriptscriptstyle 2}$  emitter area and biased with  $I_c=6 \mu$  A. The  $V_{RF}$  is observed to be 0.73 V at T=300~K, and it decreases with temperature almost linearly at a rate of -1.73 mV/K at 300 K . Such a temperature characteristic is known as Complementary to Absolute Temperature (CTAT), where the rate of change of  $V_{\scriptscriptstyle \! RF}$  against temperature is negative. When biased with different collector currents, the  $V_{\rm gg}(T)$  will vary as shown in the SPICE simulation result in Figure 1.2. To simplify our discussions in subsequent chapters, we shall assume that the BJTs are biased appropriately (with  $I_c = 6 \mu$  A), such that the  $V_{\rm \tiny RF}(T)$  can be approximated as a linear temperature function with high accuracy (unless otherwise specified). In particular. the linear temperature dependency approximation of the  $V_{BE}$  for the NPN transistor is given by

(1.8)

$$\frac{\partial V_{BE}(T)}{\partial T} = -1.73 \text{ mV/K}.$$

Similarly, the  $V_{\epsilon B}(T)$  of a PNP transistor has a linear temperature dependency given by

(1.9)

$$\frac{\partial V_{EB}(T)}{\partial T} = -1.39 \text{ mV/K}.$$

These two linearly approximated temperature characteristics of the  $V_{_{\!\mathit{BE}}}(T)$  and  $V_{_{\!\mathit{EB}}}(T)$  voltages will be applied in all our discussions unless stated otherwise. In reality, the CTAT characteristic of  $V_{_{\!\mathit{BE}}}(T)$  is not a linear temperature function as depicted in Equation  $\underline{1.4}$ , and  $\partial V_{_{\!\mathit{BE}}}(T)/\partial T$  is a high order temperature function that will cause curvature error as will be discussed in later chapters. Nevertheless, the  $V_{_{\!\mathit{BE}}}(T)$  is the PN junction voltage, which is a

process independent parameter, and is one of the robust parameters in modern CMOS processes that can be used to construct a stable and precise reference voltage.

FIGURE 1.2  $V_{BE}$  vs temperature of a NPN transistor with emitter area 25  $\mu m^2$  biased at  $I_c$  = 3,6,12  $\mu$  A.

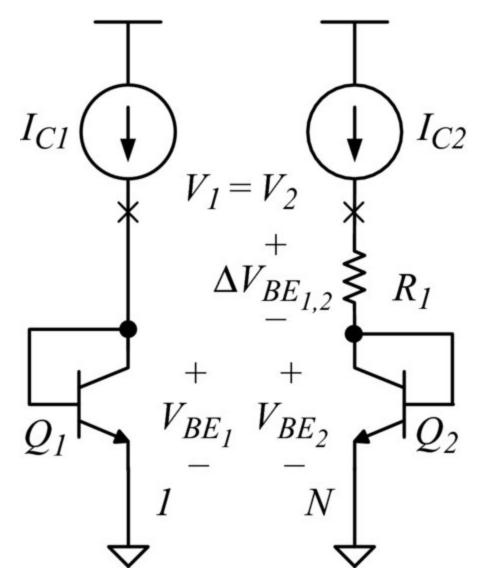

## 1.1.1 Differential $V_{s}$

As derived in Equation  $\underline{1.4}$ ,  $V_{\scriptscriptstyle BE}(T)$  is a high order function of temperature T. However, the difference of the  $V_{\scriptscriptstyle BE}(T)$  between two BJTs biased with different current densities can be well represented by a low order function or even as a linear function of the temperature T. Figure 1.3 illustrates a method to extract the differential  $V_{\scriptscriptstyle BE}$ ,  $\Delta$   $V_{\scriptscriptstyle BE_{1,2}}$ , from two BJTs  $Q_{\scriptscriptstyle 1}$  and  $Q_{\scriptscriptstyle 2}$  with emitter areas  $A_{\scriptscriptstyle E_1}$  and  $A_{\scriptscriptstyle E_2}$ , respectively (readers should note that  $V_{\scriptscriptstyle BE}(T)$  and  $V_{\scriptscriptstyle BE}$  will both be used in

this book and have exactly the same meaning). Assume  $A_{\epsilon_1}:A_{\epsilon_2}=1:N$  and the current sources will provide  $I_{c_1}=I_{c_2}$ . As a result, the current density  $J_{c_1}$  of  $Q_1$  is N times larger than the current density  $J_{c_2}$  of  $Q_2$ . This yields  $\Delta V_{BE_1,2}$  as

$$\begin{array}{l} \textbf{(1.10)} \ \ ^{\Delta V_{BE_{1,2}}} = V_{BE_1} - V_{BE_2} \\ \\ \textbf{(1.11)} \ \ = V_T \ln \left( \frac{I_{C_1}}{J_S A_{E_1}} \right) - V_T \ln \left( \frac{I_{C_2}}{J_S A_{E_2}} \right) \\ \\ \textbf{(1.12)} \ \ = V_T \ln \left( \frac{A_{E_2}}{A_{E_1}} \right) \\ \\ \textbf{(1.13)} \ \ = V_T \ln (N), \end{array}$$

where  $V_{_{\!BE_1}}$  and  $V_{_{\!BE_2}}$  are the base-emitter voltage of BJTs  $Q_{_1}$  and  $Q_{_2}$ , respectively. It can be observed that  $\Delta$   $V_{_{\!BE_{1,2}}}$  is proportional to  $V_{_{\!T}}$ , which is a linear function of T. If we rewrite Equation  $\underline{1.13}$  with respect to  $V_{_{\!T}}$ , we shall obtain

(1.14)

$$V_T = \frac{\Delta V_{BE_{1,2}}}{\ln(N)}$$

which implies the  $\Delta$   $V_{_{BE_{1,2}}}$  extraction circuit is actually a  $V_{_{7}}$  extraction circuit as well. Note that

$$\frac{\partial V_T}{\partial T} = \frac{\partial \frac{kT}{q}}{\partial T} = \frac{k}{q}$$

(1.15)  $\approx 0.09 \text{ mV/K} \text{ at } 300 \text{ K}.$

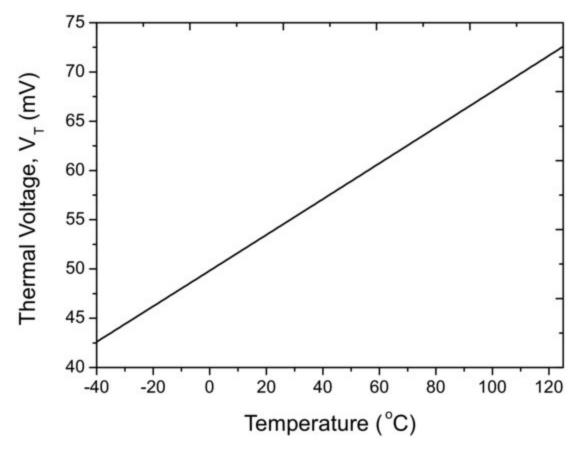

It can be observed from Equation <u>1.15</u> that the thermal voltage is an intrinsic linear *Proportional to Absolute Temperature* (PTAT) voltage. <u>Figure 1.4</u> shows the SPICE simulation result of the thermal property of  $V_{\tau}$  extracted from  $\Delta$   $V_{\rm BE_{1,2}}$  using the circuit shown in <u>Figure 1.3</u> with N=8, which demonstrates the PTAT nature of  $V_{\tau}$ .

FIGURE 1.3 Extraction of  $\Delta V_{\rm BE1.2}$  from NPN transistors.

FIGURE 1.4 Thermal property of  $V_{\tau}$  extracted from  $\Delta V_{BE_{1,2}}$  with emitter area ratio N=8 using the circuit shown in Figure 1.3.

The PTAT voltage  $V_{\tau}$  and the CTAT voltage  $V_{\scriptscriptstyle RF}$  are commonly used as the thermal elements to generate a temperature insensitive reference voltage. Temperature Coefficient (TC) reference voltage can be obtained by compensating the CTAT voltage  $V_{\scriptscriptstyle RF}$  with a weighted PTAT voltage  $V_{\tau}$  (The temperature coefficient will be formally defined in Section 2.1.2). The compensation obtained in the form of voltage sum can be easily by the resistor network. implemented However, the resistance of the resistor implemented in the CMOS process is process sensitive, thus imposing another adverse effect on the obtained reference voltage. The derivation of the weighting factor and the methods to compensate the adverse effects from the process variation problem will be discussed in Chapter 4.

# 1.2 Metal-Oxide Semiconductor Field-Effect Transistor

metal-oxide semiconductor field-effect transistor, MOSFET, has proved extremely popular compared to the BJT. This is because of the compact layout and simple structure of the MOSFET. In this text, we shall mainly concentrate on the enhancement-mode MOSFET, including both the N channel MOSFET (NMOS) and P -channel MOSFET (PMOS), since they are the most commonly available MOSFET devices in modern CMOS foundry services. Other types of MOS transistors will be discussed over the course of voltage reference circuit development in later chapters when such devices are applied. Showing in Figure 1.5 are the symbols of the MOSFETs that we shall use in this text. Physically, the MOSFET is a four-terminal device with a source, drain, gate, and substrate terminals. The substrate terminals of the NMOS and PMOS transistors are usually connected to GND and  $V_{nn}$  , respectively. We shall use the simplified threeterminal symbols as shown in Figure 1.5 throughout the book. The arrows beside the MOSFET symbols illustrate the direction of the current that is flowing through the drain and source terminals. The silicon layout of an NMOS transistor is shown in Figure 1.5(c). To understand the operation of the MOSFET device, let us consider the physical structure of a NMOS transistor as shown in Figure 1.6, where the NMOS transistor is fabricated directly on the P -type substrate, with  $N^+$  regions forming the drain and source terminals, and with electrons as charge carriers. With the source terminal being grounded, and a positive voltage applied to the gate terminal, the positive voltage at the gate terminal attracts the negative electrons in the P-type substrate to accumulate under the gate terminal and repel the positive holes downwards, thus inverting the substrate surface from P -type to N -type. As a result, this layer is also known as