## 1V CMOS $G_m$ -C Filters

### ANALOG CIRCUITS AND SIGNAL PROCESSING SERIES

Consulting Editor: Mohammed Ismail. Ohio State University

For other titles published in this series, go to www.springer.com/series/7381

Tien-Yu Lo · Chung-Chih Hung

# 1V CMOS $G_m$ -C Filters

**Design and Applications**

Dr. Tien-Yu Lo MediaTek Inc. No.1, Dusing Rd. 1 Hsinchu 30078 Hsinchu Science Park Taiwan tienyu.lo@gmail.com Assoc. Prof. Chung-Chih Hung National Chiao Tung University Department of Electrical Engineering 1001 University Road Hsinchu 300 Taiwan cchung@mail.nctu.edu.tw

ISBN 978-90-481-2409-1 e-ISBN 978-90-481-2410-7 DOI 10.1007/978-90-481-2410-7 Springer Dordrecht Heidelberg London New York

Library of Congress Control Number: PCN applied for

© Springer Science+Business Media B.V. 2009

No part of this work may be reproduced, stored in a retrieval system, or transmitted in any form or by any means, electronic, mechanical, photocopying, microfilming, recording or otherwise, without written permission from the Publisher, with the exception of any material supplied specifically for the purpose of being entered and executed on a computer system, for exclusive use by the purchaser of the work.

Printed on acid-free paper

Springer is part of Springer Science+Business Media (www.springer.com)

### **Preface**

There are growing demands for low-voltage circuits and systems, especially for system-on-a-chip applications. When switched to low supply voltage, digital circuits do not suffer the degradation in performance. On the other hand, the circuit performance of analog circuits are strongly affected by reduced supply voltage. In addition, chip area should also be taken into consideration to reduce the cost of advanced multi-function SOC design. Therefore, there is urgent need to develop new design techniques for analog circuits at 1-V supply.

In Chapter 2, novel transconductors with the applications for wireless and wireline systems are introduced. The transconductor is a basic building block for analog circuits, such as the  $G_m$ -C filter, continuous-time delta-sigma modulator, voltage-controlled oscillator, and multiplier. First, the configuration of a linearized transconductor for low-voltage and high-frequency applications is proposed. By using double pseudo-differential pairs and the source degeneration structure under nano-scale CMOS technology, the nonlinearity caused by short channel effect from small feature size can be minimized. Then, another transconductor with pseudo-differential structures is proposed. The linearity is improved by mobility compensation techniques as the device size is scaled down to achieve high-speed operation. Short channel effects in the nano-scale technology are discussed and eliminated, and the results show superior performance even at high-speed operation. Finally, a transconductor with the specific target for ADSL2+ application is discussed. A precise model is adopted to eliminate short channel effects and high linearity performance can thus be achieved.

Chapter 3 focuses on the basic concept of the  $G_m$ -C implementation. A  $G_m$ -C filter with a fifth-order Elliptic prototype and a wide tuning range for very low frequency is discussed. The transconductor can work from the weak inversion region to the strong inversion region to maximize the transconductance tuning range. The transconductance can be tuned by changing its bias current. Through the use of switching technology, the filter can be applied to biomedical systems, audio systems and part of wireless systems.

Three multi-mode channel selection filters for the Zero-IF direct conversion receiver are presented in Chapter 4. The specific transconductors with required

viii Preface

functions are designed through the use of a third-order Butterworth prototype. The proposed circuit first uses the forward voltage follower structure and an active resistor to implement the linear transconductor. The wide tuning range would be suitable for the specifications of IEEE 802.11a/b/g Wireless LANs, Wideband CDMA, cdma2000, and Bluetooth. Then, the other transconductor is presented. The transconductor includes a voltage-to-current converter and a current multiplier. Voltage-to-current conversion employs linear-region MOS transistors and the circuit features high linearity over a wide input swing. The current multiplier which operates in the weak inversion region provides a wide transconductance tuning range without degrading the linearity. The tuning range and the linearity performance would be suitable for the wireless specifications of GSM, Bluetooth, cdma2000, and Wideband CDMA. Finally, another transconductor uses the same concept as that of the previous one. Linear-region MOS transistors are employed to perform the voltage-to-current conversion. The wide tuning range can be achieved by the current multiplier following the linear voltage-to-current converter.

Two high-speed filters with a fourth-order equiripple prototype are analyzed in Chapter 5. The high-speed filter can be used for pulse signal systems. One is designed for the hard disk storage systems, and a novel automatic tuning circuit is also implemented to account for variations in process and temperature. A high-speed transconductor with the inverter structure is realized. Transconductance tuning can be achieved by adjusting the bulk voltage using the Deep-NWELL technology. Then, a high-performance  $G_m$ -C equiripple linear phase low-pass filter for UWB wireless application is presented. The proposed transconductor is designed under low supply voltage while its gain, excess phase, and linearity are well maintained.

This book is organized based upon the Ph.D. dissertation in National Chiao Tung University, Taiwan. It includes details and measurement results for each research project, and the analyses made with circuits operating at 1-V supply. The projects were supported by the National Science Council of Taiwan, while the chips were fabricated by the National Chip Implementation Center of Taiwan.

This book would not been published without the help and kindness of many individuals. First of all, we would like to thank Prof. Mohammed Ismail of the Ohio State University for his helpful comments. He is indeed a world leader in the research and education of analog and RF circuit designs. Some sections are enlightened by his influential work. We would like to express our gratitude to Mr. Chih-Lung Kuo, who has made significant contribution to this book. He spent days and nights typesetting and editing the initial version. A special thank goes to all the members of NCTU Analog Integrated Circuit Lab for their generous assistance and insightful technical discussion over the years. Finally, the first author would like to thank Dr. Hung-Sung Li at MediaTek Inc. for his guidance, encouragement, and support.

Tien-Yu Lo Chung-Chih Hung

### **Contents**

|   |            | O      |                                                    |    |

|---|------------|--------|----------------------------------------------------|----|

| 1 | Motivation |        |                                                    | 1  |

|   | 1.1        |        | luction                                            |    |

|   | 1.2        | Applio | cations                                            | 2  |

|   | 1.3        |        | ization                                            |    |

| 2 | Tra        | nscond | uctor                                              | 5  |

|   | 2.1        | Introd | luction                                            | 5  |

|   | 2.2        | Revie  | w of CMOS Transconductors                          |    |

|   |            | 2.2.1  | The Source Degenerated Transconductor              | 5  |

|   |            | 2.2.2  | The Constant Drain-Source Transconductor           | 8  |

|   |            | 2.2.3  | The Pseudo-Differential Transconductor             | 9  |

|   |            | 2.2.4  | The Multiple Input Floating-Gate Transconductor    | 12 |

|   | 2.3        | The 4  | 0 MHZ Double Differential-Pair CMOS                |    |

|   |            | Transo | conductor With $-60$ DB IM3                        | 14 |

|   |            | 2.3.1  | Introduction                                       | 14 |

|   |            | 2.3.2  | Nonlinearity Analysis of Saturated MOS Transistors | 14 |

|   |            | 2.3.3  | Proposed Transconductor Circuit                    |    |

|   |            | 2.3.4  | Non-Ideality Analysis of the Implementation        | 23 |

|   |            | 2.3.5  | Experimental Results                               |    |

|   |            | 2.3.6  | Summary                                            | 27 |

|   |            | 2.3.7  | Analysis for Circuit at 1-V Supply                 | 28 |

|   | 2.4        | A 501  | MHZ Pseudo-Differential Transconductor             |    |

|   |            | With I | Mobility Reduction Compensation                    | 29 |

|   |            | 2.4.1  | Introduction                                       |    |

|   |            | 2.4.2  | The Proposed Transconductor Cell                   | 29 |

|   |            | 2.4.3  | Experimental Results                               |    |

|   |            | 2.4.4  | Summary                                            | 37 |

x Contents

|   | 2.5     | Linear         | r CMOS Transconductor in Nano-Scale CMOS Technology              |      |

|---|---------|----------------|------------------------------------------------------------------|------|

|   |         | 2.5.1          | Introduction                                                     | . 38 |

|   |         | 2.5.2          | Operational Transconductance Amplifier                           | . 39 |

|   |         | 2.5.3          | Experimental Results                                             | . 43 |

|   |         | 2.5.4          | Summary                                                          | . 46 |

| 3 | $G_m$ - | C Filte        | er                                                               | . 47 |

|   | 3.1     | Introd         | luction                                                          | . 47 |

|   | 3.2     | Imple          | mentation of the $G_m$ - $C$ Filter                              | . 47 |

|   |         | 3.2.1          | Integrator                                                       | . 47 |

|   |         | 3.2.2          | Programmable Integrator                                          |      |

|   |         | 3.2.3          | Filter Synthesis Methods                                         |      |

|   |         | 3.2.4          | Effect of Integrator Non-Idealities in Filter                    |      |

|   | 3.3     | A Wio          | de Tuning Range $G_m$ - $C$ Continuous-Time Analog Filter        |      |

|   |         | 3.3.1          | Introduction                                                     |      |

|   |         | 3.3.2          | The Proposed Transconductor Cell                                 |      |

|   |         | 3.3.3          | The Equivalent Resistor $R_{EO}$                                 |      |

|   |         | 3.3.4          | Filter Architecture                                              |      |

|   |         | 3.3.5          | Experimental Results                                             | . 79 |

|   |         | 3.3.6          | Summary                                                          |      |

|   |         | 3.3.7          | Analysis for Circuit at 1-V Supply                               |      |

| 4 | Mad     | ti mad         | e Channel Selection Filter for Wireless Application              | . 89 |

| 4 | 4.1     |                | luction                                                          |      |

|   | 4.2     |                | IF Receiver                                                      |      |

|   | 4.3     |                | -C Continuous-Time Analog Filter for Multi-mode                  | . 09 |

|   | 4.5     |                | ess Applications                                                 | . 90 |

|   |         | 4.3.1          | Introduction                                                     |      |

|   |         | 4.3.1          | Proposed Transconductor Circuit.                                 |      |

|   |         | 4.3.2          | -                                                                |      |

|   |         | 4.3.4          | The Equivalent Resistor and the CMFB Circuit Filter Architecture |      |

|   |         | 4.3.4          | Results                                                          |      |

|   |         | 4.3.6          |                                                                  |      |

|   |         | 4.3.7          | Summary                                                          |      |

|   | 4.4     |                | Analysis for Circuit at 1-V Supply                               | . 90 |

|   | 4.4     |                | -Mode $G_m$ -C Channel Selection Filter                          | 00   |

|   |         |                | obile Applications                                               |      |

|   |         | 4.4.1          | Introduction                                                     |      |

|   |         | 4.4.2          | 1                                                                |      |

|   |         | 4.4.3          | Filter Architecture and Measurement Result                       |      |

|   | 4.7     | 4.4.4          | Summary                                                          | .108 |

|   | 4.5     |                | de Tuning Range $G_m$ - $C$ Filter for Multi-mode                | 100  |

|   |         |                | t-Conversion Wireless Receivers                                  |      |

|   |         | 4.5.1          | Introduction                                                     |      |

|   |         | 4.5.2<br>4.5.3 | The Proposed Transconductor Circuit                              |      |

|   |         | 433            | Filler Architecture and Measurement Results                      | 116  |

Contents xi

|    |       | 4.5.4   | Summary                                          | 119 |

|----|-------|---------|--------------------------------------------------|-----|

|    |       | 4.5.5   | Analysis for Circuit at 1-V Supply               | 120 |

| 5  | Hig   | h Speed | I Filter with Automatic Tuning Circuit           | 123 |

|    | 5.1   |         | luction                                          |     |

|    | 5.2   | Linear  | r Phase Filter                                   | 123 |

|    |       | 5.2.1   | Filter Transfer Function                         | 124 |

|    |       | 5.2.2   | Group Delay Sensitivity                          | 125 |

|    | 5.3   | Auton   | natic Tuning Circuit                             | 126 |

|    |       | 5.3.1   | Direct Tuning Architecture                       | 127 |

|    |       | 5.3.2   |                                                  |     |

|    | 5.4   | A 1 G   | HZ Equiripple Low-Pass Filter with a High-Speed  |     |

|    |       |         | natic Tuning Scheme                              | 130 |

|    |       | 5.4.1   | Introduction                                     | 130 |

|    |       | 5.4.2   | Operational Transconductance Amplifier           | 131 |

|    |       | 5.4.3   | Filter Architecture and Automatic Tuning Circuit | 135 |

|    |       | 5.4.4   | Measurement Results                              |     |

|    |       | 5.4.5   | Summary                                          |     |

|    |       | 5.4.6   | Analysis for Circuit at 1-V Supply               |     |

|    | 5.5   | A $G_m$ | -C Low-Pass Filter for UWB Wireless Application  |     |

|    |       | 5.5.1   | Introduction                                     |     |

|    |       | 5.5.2   | Proposed Operational Transconductance Amplifier  |     |

|    |       | 5.5.3   | Common-Mode Control Circuit                      |     |

|    |       | 5.5.4   | Filter Implementation and Measurement Results    | 146 |

|    |       | 5.5.5   | Summary                                          |     |

| 6  | Con   | clusion | <b>IS</b>                                        | 151 |

| Re | feren | ices    |                                                  | 153 |

| Ab | out t | he Autl | hors                                             | 157 |

## **List of Figures**

| 1.1  | The filter operation frequency for various applications                 | 2  |

|------|-------------------------------------------------------------------------|----|

| 2.1  | The implementation of the source degeneration transconductor:           |    |

|      | (a) single current source (b) dual current source                       | 6  |

| 2.2  | The modified source degeneration transconductor                         |    |

| 2.3  | The transconductor by using linear region transistor as inputs          | 8  |

| 2.4  | The regulated control loop amplifier                                    | 9  |

| 2.5  | The differential transconductor: (a) fully-differential.                |    |

|      | (b) pseudo-differential                                                 | 10 |

| 2.6  | The common-mode feedforward circuit                                     |    |

| 2.7  | The block diagram of the attenuation technique                          |    |

| 2.8  | The structure of MIFG NMOS transistor                                   |    |

| 2.9  | The transconductor implemented by MIFG NMOS transistors                 | 13 |

| 2.10 | The pseudo-differential circuit by taking short channel effects into    |    |

|      | consideration: (a) short channel transistor (b) long channel transistor | 16 |

| 2.11 | Nonlinearity cancellation using double pseudo-differential pairs        |    |

|      | with degeneration resistors                                             | 16 |

| 2.12 | Optimal parameter evaluation for the reduced transconductance           | 18 |

| 2.13 | Optimal parameter evaluation for the third-order harmonic component     | 19 |

|      | Contour plot for the third-order harmonic component                     |    |

|      | under transconductance tuning                                           | 20 |

| 2.15 | Proposed transconductor circuit                                         | 21 |

| 2.16 | Simulated transconductance tuning range                                 | 21 |

| 2.17 | The common-mode control system                                          | 22 |

| 2.18 | Die microphotograph                                                     | 25 |

| 2.19 | Measured two tone inter-modulation distortion                           | 26 |

| 2.20 | Measured two tone inter-modulation distortion with respect              |    |

|      | to input signal frequency                                               | 26 |

| 2.21 | Simulated transconductance tuning range at 1-V supply                   |    |

| 2.22 | Nonlinearity cancellation mechanism.                                    | 30 |

xiv List of Figures

| 2.23 | Mobility compensation technique: (a) basic pseudo-differential CMOS         |    |

|------|-----------------------------------------------------------------------------|----|

|      | pair (b) mobility compensation in the pseudo-differential structure         | 30 |

| 2.24 | Proposed OTA circuit                                                        | 33 |

| 2.25 | Large signal simulation of the proposed circuit                             | 34 |

|      | Die microphotograph                                                         |    |

| 2.27 | The output current versus input voltage over the tuning range               | 36 |

| 2.28 | Measured two tone inter-modulation distortions                              | 37 |

| 2.29 | The differential transconductor                                             | 40 |

| 2.30 | The modified transconductor by using saturated transistors                  | 40 |

| 2.31 | The modified transconductor by using weak inversion transistors             | 42 |

| 2.32 | The simulated Gm range of the proposed transconductor                       | 43 |

|      | The chip micrograph                                                         | 44 |

| 2.34 | Measured third-order harmonic distortion: (a) the differential              |    |

|      | transconductor                                                              | 44 |

| 2.34 | (continued) (b) the modified transconductor by using                        |    |

|      | saturated transistors (c) the modified transconductor by using              |    |

|      | weak inversion transistors                                                  | 45 |

|      |                                                                             |    |

| 3.1  | The single-ended integrator                                                 | 48 |

| 3.2  | The fully-differential integrator: (a) single capacitor (b) dual capacitors |    |

| 3.3  | The gain and phase of ideal (dashed) and non-ideal (solid) integrator       | 49 |

| 3.4  | Integrator: (a) the integrator with maximum unity-gain frequency            |    |

|      | (b) the integrator with constant-Gm design (c) the integrator               |    |

|      | with constant-C <sub>L</sub> design                                         |    |

| 3.5  | The lossy integrator                                                        |    |

| 3.6  | The biquad section                                                          |    |

| 3.7  | The sixth-order Elliptic low-pass passive filter                            | 54 |

| 3.8  | The SFG synthesis of the LC network; (a) passive prototype                  |    |

|      | (b) implementation of (3.16) (c) implementation of (3.17)                   |    |

|      | (d) implementation of (3.18)                                                | 55 |

| 3.9  | The SFG synthesis of the input R and output RC network;                     |    |

|      | (a) equation (3.19) (b) equation (3.20)                                     |    |

|      | The $G_m$ - $C$ implementation of passive network shown in Fig. 3.9         | 56 |

| 3.11 | Noise model; (a) the biquad bandpass filter including integrator noise      |    |

|      | model (b) the bandpass passive prototype with integrator                    |    |

|      | noise model                                                                 | 60 |

| 3.12 | The illustration of input and output intercept point                        |    |

|      | with the unit of decibel                                                    |    |

|      | The proposed transconductor circuit                                         |    |

|      | Equivalent resistor circuit.                                                |    |

|      | Final implementation of the proposed transconductor circuit                 |    |

|      | $V_{mode}$ switching circuit for the proposed transconductor                |    |

|      | Simulated linearity performance of the equivalent resistor                  |    |

|      | Fifth-order elliptic RLC ladder network prototype                           |    |

| 3 10 | Fifth-order Ellintic low-pass G -C filter                                   | 79 |

List of Figures xv

| 3.20 | The measurement results of the proposed transconductor circuit:          |      |

|------|--------------------------------------------------------------------------|------|

|      | (a) transconductor in the weak inversion region (b) transconductor       |      |

|      | in the multi-inversion regions: the input stage stays in the weak        |      |

|      | inversion region while the output stage operates from the weak           |      |

|      | inversion region to the strong inversion region                          | . 81 |

| 3.20 | (continued) (c) transconductor in the strong inversion region            |      |

|      | (d) transconductor in the multi-inversion regions: the input stage stays |      |

|      | in the strong inversion region while the output stage operates           |      |

|      | from the strong inversion region to the weak inversion region            | . 82 |

| 3.21 | Measured frequency responses over the tuning range                       |      |

|      | Measured IM3 values at cutoff frequency                                  |      |

|      | Die microphotograph.                                                     |      |

|      | FOM comparison with previously published filters                         |      |

|      | Simulated transconductance tuning range (weak inversion region)          |      |

| 0.20 | at 1-V supply: (a) the equivalent active resistor (b) passive            |      |

|      | poly resistor                                                            | . 87 |

| 3.26 | Simulated transconductance tuning range (saturation region)              | ,    |

| 3.20 | at 1-V supply                                                            | . 88 |

|      | w 1 + 5uppij                                                             | . 00 |

| 4.1  | The basic diagram of the direct-conversion receiver                      | . 90 |

| 4.2  | Proposed transconductor circuit: (a) implementation of transconductor    |      |

|      | (b) open loop model of the FVF circuit                                   | . 91 |

| 4.3  | The equivalent resistor circuit                                          |      |

| 4.4  | The common-mode feedback circuit                                         |      |

| 4.5  | The $G_m$ - $C$ realization of the third-order Butterworth filter        |      |

| 4.6  | Gm variation of the proposed transconductor                              |      |

| 4.7  | The frequency response of the proposed multi-mode filter                 |      |

| 4.8  | Gm variation of the proposed transconductor at 1-V supply                |      |

| 4.9  | Basic diagram of the transconductor                                      |      |

| 4.10 | The voltage-to-current cell                                              |      |

| 4.11 | The high linearity current multiplier                                    |      |

| 4.12 | The simulated Gm range of the proposed transconductor                    |      |

|      | The final implementation of the proposed transconductor                  |      |

|      | with the CMFB circuit.                                                   | .106 |

| 4.14 | The chip micrograph                                                      |      |

|      | The measured frequency responses of the proposed                         |      |

|      | multi-mode filter                                                        | .107 |

| 4.16 | Implementation of transconductor: (a) the conventional transconductor    |      |

|      | (b) the MOSFET-only transconductor (c) the differential                  |      |

|      | transconductor                                                           | .109 |

| 4.17 | The concept of a wide tuning range transconductor                        |      |

|      | Final implementation of the proposed transconductor                      |      |

|      | with the CMFB circuit.                                                   | .114 |

| 4.19 | The simulated Gm range of the proposed transconductor                    |      |

|      | The chip micrograph.                                                     |      |

|      |                                                                          |      |

xvi List of Figures

| 4.21       | Two-tone test of the proposed transconductor                            | 117 |

|------------|-------------------------------------------------------------------------|-----|

| 4.22       | The measured frequency responses of the proposed                        |     |

|            | multi-mode filter                                                       | 118 |

| 4.23       | The simulated Gm range of the proposed transconductor at 1-V supply .   | 120 |

| <i>5</i> 1 | Cincilia de anticontrar estable front en d                              | 104 |

| 5.1        | Simplified architecture of HDD front-end                                |     |

| 5.2        | Direct tuning scheme.                                                   |     |

| 5.3        | Indirect tuning scheme.                                                 | 128 |

| 5.4        | Frequency tuning circuit by using single transconductor:                | 120 |

| 5.5        | (a) resistor based tuning (b) switch based tuning                       |     |

|            | Frequency tuning based on the VCO.                                      |     |

| 5.6<br>5.7 | Frequency tuning based on the VCF.                                      |     |

|            | The high speed transconductor circuit.                                  | 131 |

| 5.8        | Circuit implementation: (a) negative output resistance circuit for gain | 124 |

| 5.9        | enhancement (b) transconductance tuning circuit                         |     |

|            | The fourth-order equiripple linear phase filter                         |     |

|            | The modified automatic tuning scheme.                                   |     |

|            | The measured frequency response of the proposed filter                  |     |

|            | The measured group delay of the proposed filter                         |     |

|            | Two tone inter-modulation of the filter                                 |     |

|            | Die micrograph                                                          |     |

|            | The transconductance of the proposed transconductor at 1-V supply       |     |

|            | Linearized low voltage transconductor circuit                           |     |

|            | The modified low voltage transconductor circuit                         |     |

|            | The common-mode control system                                          |     |

|            | The fourth-order equiripple linear phase filter                         |     |

|            | Die micrograph                                                          | 148 |

| 5.21       | The magnitude response and the group delay of the fourth-order          |     |

|            | equiripple linear phase $G_m$ - $C$ filter                              |     |

| 5.22       | Measured two tone inter-modulation distortion                           | 149 |

### **List of Tables**

|     | Comparison with previously reported works                    |     |

|-----|--------------------------------------------------------------|-----|

| 2.2 | Comparison of previously reported works                      | 38  |

| 3.1 | Performance summary of the fabricated prototype              | 85  |

| 4.1 | Performance summary of this work                             | 97  |

| 4.2 | Performance summary of this work                             | 107 |

| 4.3 | Performance summary of this work                             | 119 |

| 4.4 | Comparison with previously reported works                    | 119 |

| 5.1 | The denominator of equiripple linear phase transfer function | 125 |

| 5.2 | Comparison of previously reported works                      | 140 |

|     | Comparison of previously reported works                      |     |

# Chapter 1 Motivation

#### 1.1 Introduction

Low-voltage VLSI circuits have received significant attention in recent years. The supply voltage has decreased following the advancement of process technology, and the operation frequency of CMOS can also go up higher than 100 GHz. The demands for nano-scale applications are mainly classified into technology-driven, design-driven, and market-driven. They are mainly to reduce the minimum feature size to scale down the chip area, to fabricate millions of transistors on a single chip to save cost, and to the increase market demands for communication electronic products. These demands seem to be independent of each other. However, the advances in VLSI technology, circuit design, and product market are actually interrelated.

In the past decade, CMOS technology has played a major role in the rapid advancement and the increased integration of VLSI systems. CMOS devices feature high input impedance, extremely low offset switches, high packing density, low switching power consumption, and thus can be easily scaled. The minimum feature size of a MOS transistor has been decreasing [1-3]. Current VLSI technology is scaled down to around 90 nm. Scaling down the transistor sizes can then integrate more circuit components in a single chip, so the circuit area and thus its cost will be reduced. Besides this economic consideration, smaller geometry usually lowers the parasitic capacitance, which leads to higher operating speed. When a MOS transistor size is decreased, not only its channel length and width are reduced, but also the thickness of the gate oxide. As a MOS transistor has a thinner gate oxide, in order to prevent the transistor from breakdown due to higher electrical field across the gate oxide and to ensure its reliability, the supply voltage needs to be reduced [4–8]. Since the digital circuits are becoming more and more popular, the computer-aided design tools for digital circuits are getting matured, the digital circuits are certainly occupying most of the fabricated chip area, and the electrical characteristics of MOS transistors are getting optimized mainly for digital circuits. Switching to use nanoscale devices, digital circuits do not suffer the degradation of their performances too much.

2 1 Motivation

On the other hand, for analog circuits, the circuit performances, such as gain, dynamic range, speed, bandwidth, linearity, etc., are strongly affected by using nano-scale technology. Therefore, new design techniques for nano-scale analog circuits are required to be developed. Moreover, since we are living in an analog world, it is inevitable to use analog signal processing. Modern analog and mixed-signal VLSI applications in areas such as telecommunications, smart sensors, battery-operated consumer electronics and artificial neural computation require CMOS analog design solutions. Thus, analog signal and information processing in nano-scale technology is really a field requiring more devotion.

#### 1.2 Applications

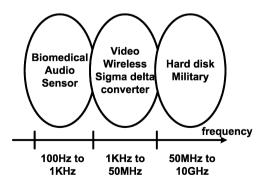

In the systems that interface with real word, the processed signal would be measured with unwanted noise. A filter is usually used to get rid of the unwanted noise and to reject the surrounding interface. Thus, filters are important block for specified frequency of signals and they are essential for many applications. They can be used to band-limit signals in wireline and wireless communication systems. These filters operate on continuous-time fashion because the systems interface with real analog world. Figure 1.1 shows the required low-pass filter for specified applications.

There are two kinds of the filters: digital filters and analog filters. The analog filters process the continuous data rather than the digital data for digital filters. The analog filters can be further divided into passive filters and active filters. The elements of a passive filter are passive, and a passive filter includes resistors, capacitors, inductors, and transformers. On the contrary, the active filters include active devices. A large area is required for the passive filter, and then the active filter is more suitable in CMOS technology.

Active filters can be classified into Active-RC, Switched-Capacitor,  $G_m$ -C, and LC filters. The Active-RC and Switched-Capacitor filters are only suitable for low to medium frequency applications. For high frequencies, the settling problem of

Fig. 1.1 The filter operation frequency for various applications